И2Ц магистрала — додела, уређај, пренос података, адресирање

Приликом креирања електронског кола, многи програмери се суочавају са потребом да користе велики број средњих чипова за упаривање, узорковање и адресирање његових појединачних блокова. Да би се смањио број помоћних чипова, Пхилипс је још 1980-их предложио двожични двосмерни И2Ц серијски мрежни интерфејс, дизајниран посебно за управљање више чипова унутар једног уређаја.

Данас само Пхилипс производи више од стотину И2Ц компатибилних уређаја за електронску опрему са широким спектром намена: меморију, системе видео процесора, аналогно-дигиталне и дигитално-аналогне претвараче, драјвере за екране итд.

И2Ц магистрала је модификација протокола за серијску размену података способна да преноси серијске 8-битне податке у уобичајеном „брзом“ режиму брзином од 100 до 400 кбпс. Процес размене података је овде имплементиран на само две жице (не рачунајући заједничку жицу): СДА линију за податке и СЦЛ линију за синхронизацију.

Сабирница постаје двосмерна због чињенице да каскаде излаза уређаја повезаних на магистралу имају отворене колекторе или канале, чиме се реплицира И ожичење. Као резултат тога, магистрала минимизира број веза између чипова, остављајући мање потребних пинова и трагова на плочи. Као резултат, сама плоча испада једноставнија, компактнија и технолошки напреднија у производњи.

Овај протокол вам омогућава да онемогућите декодере адреса и другу логику екстерног преговарања. Број чипова који могу истовремено да раде на И2Ц магистрали ограничен је њеним капацитетом — максимално 400 пФ.

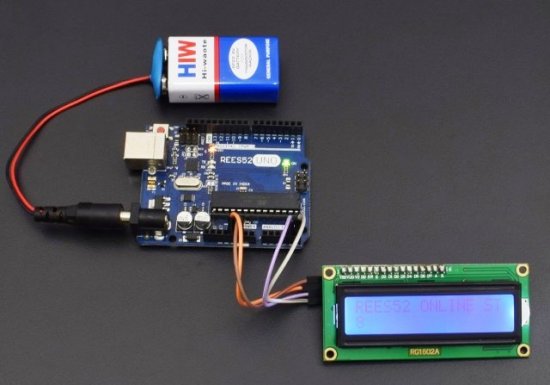

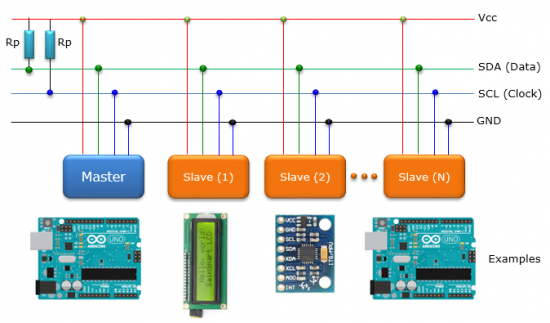

ИЦ-ови компатибилни са И2Ц имају алгоритам за сузбијање хардверског шума како би се осигурао интегритет података чак иу присуству јаких сметњи. Такви уређаји имају интерфејс који омогућава микроколама да међусобно комуницирају чак и када су им напони напајања различити. На слици испод можете се упознати са принципом повезивања неколико микрокола кроз заједничку магистралу.

Сваки од уређаја прикључених на магистралу има своју јединствену адресу, њоме се одређује и у складу са наменом уређаја може да ради као пријемник или као предајник. Приликом преноса података ови уређаји могу бити мастер (мастер) или славе (славе). Мастер је уређај који покреће пренос података и генерише такт сигнале на СЦЛ линији. Славе, у односу на мастер, је одредишни уређај.

У било ком тренутку рада на И2Ц магистрали, само један уређај може да делује као мастер; генерише сигнал на СЦЛ линији.Мастер може бити или главни пријемник или главни предајник.

У принципу, магистрала дозвољава неколико различитих мастера, али намеће ограничења на карактеристике формирања контролних сигнала и праћења статуса магистрале; то значи да више мастера може истовремено да почне да емитује, али се конфликти ове врсте елиминишу захваљујући арбитражи, односно начину на који се мастер понаша када открије да је магистралу заузета другим мастером.

Синхронизација пара уређаја је обезбеђена чињеницом да су сви уређаји повезани на магистралу, формирајући "АНД" ожичење. У почетку, СДА и СЦЛ сигнали су високи.

СТАРТ и СТОП

Размена почиње тако што мастер генерише стање «СТАРТ»: на СДА линији сигнал иде из високог у ниско стање, док СЦЛ линија има стабилан високи ниво. Сви уређаји повезани на магистралу ову ситуацију доживљавају као команду за покретање размене.

Сваки мастер генерише појединачни такт сигнал на СЦЛ линији када преноси податке на магистралу.

Размена се завршава формирањем СТОП стања од стране мастера: на СДА линији сигнал се мења са ниског на високи, док СЦЛ линија има стабилан високи ниво.

Возач увек делује као извор СТАРТ и СТОП сигнала. Чим је сигнал «СТАРТ» фиксиран, то значи да је линија заузета. Линија је слободна када се детектује СТОП сигнал.

Одмах након декларисања СТАРТ стања, мастер пребацује СЦЛ линију на ниско и шаље најзначајнији бит првог бајта поруке на СДА линију. Број бајтова у поруци није ограничен.Промене на СДА линији су омогућене само када је ниво сигнала на СЦЛ линији низак. Подаци су валидни и не треба их мењати само када је синхронизациони пулс висок.

Потврда да је бајт са главног предајника примљен од стране подређеног пријемника врши се постављањем посебног бита потврде на СДА линији након што је примљен осми бит података.

ПОТВРДУ

Дакле, слање 8 битова података од предајника до пријемника завршава се додатним импулсом на СЦЛ линији када пријемни уређај падне на ниско на СДА линији, што указује да је примио цео бајт.

Потврда је саставни део процеса преноса података. Мастер генерише синхронизациони импулс. Предајник шаље ниско стање СДА док је сат за потврду активан. Док је синхронизациони пулс висок, пријемник мора да држи СДА низак.

Ако одредишни славе не потврди своју адресу, на пример зато што је тренутно заузет, линија података мора да се држи високо. Мастер тада може дати СТОП сигнал за прекид слања.

Ако пријем врши главни пријемник, онда је дужан да обавести подређени предајник након завршетка преноса – не потврђивањем последњег бајта. Подређени предајник ослобађа линију података тако да мастер може издати СТОП сигнал или понављајући СТАРТ сигнал.

Синхронизација уређаја је обезбеђена чињеницом да се прикључци на СЦЛ линију врше по принципу "АНД".

Мастер нема искључиво право да контролише прелазак СЦЛ линије са ниске на високу.Ако је славе-у потребно више времена да обради примљени бит, може независно држати СЦЛ ниским док не буде спреман да прими следећи бит података. СЦЛ линија у таквој ситуацији ће бити ниска за време трајања најдужег синхронизационог импулса ниског нивоа.

Уређаји са најнижим трајним ниским нивоом ће остати неактивни док се дужи период не заврши. Када сви уређаји заврше период ниске синхронизације, СЦЛ ће постати висок.

Сви уређаји ће почети да раде на високом такту и први уређај који заврши свој период биће први који ће поставити ниску СЦЛ линију. Као резултат тога, трајање ниског стања СЦЛ биће одређено најдужим ниским стањем синхронизационог импулса једног од уређаја, а трајање високог стања ће бити одређено најкраћим периодом синхронизације једног од уређаја. уређаја.

Пријемници могу користити сигнале синхронизације као средство за контролу преноса података на нивоу бита и бајтова.

Ако је уређај способан да прима бајтове великом брзином, али му је потребно одређено време да ускладишти примљени бајт или да се припреми за пријем следећег бајта, може да настави да држи СЦЛ низак након пријема и потврде бајта, приморавајући предајник у стање приправности.

Микроконтролер без уграђених хардверских кола, на пример на нивоу бита, може да успори брзину такта повећањем трајања њиховог ниског стања. Као резултат тога, брзина преноса главног уређаја ће бити одређена брзином уређаја. спорији уређај.

АДРЕСИРАЊЕ

Сваки уређај повезан на И2Ц магистралу има јединствену програмску адресу на коју му се мастер обраћа слањем одређене команде. Микро кола истог типа карактерише селектор адреса, реализован или у облику дигиталних улаза селектора, или у аналогном облику. Адресе се деле на адресни простор уређаја повезаних на магистралу.

Нормални режим подразумева седмобитно адресирање. Адресирање функционише на следећи начин: после команде «СТАРТ», мастер шаље први бајт, који одређује који је славе уређај потребан за комуникацију са мастером. Постоји и заједничка адреса позива која дефинише све уређаје на магистрали, сви уређаји (теоретски) одговарају на њу потврдом, али у пракси је то ретко.

Дакле, првих седам битова првог бајта су славе адреса. Најмањи битни бит, осми, означава правац слања података. Ако постоји «0», онда ће информација бити записана од мастера до овог славе-а. Ако је «1», информације ће читати мастер са овог славе-а.

Након што мастер заврши слање бајта адресе, сваки славе упоређује своју адресу са њим. Свако са истом адресом је славе и дефинисан је као подређени предајник или славе пријемник, у зависности од вредности најмање значајног бита адресног бајта.

Подређена адреса може да садржи фиксне и програмабилне делове. Доста често велики број уређаја истог типа ради у једном систему, тада програмабилни део адресе омогућава коришћење максимално истог типа уређаја на магистрали. Колико битова у адресном бајту се може програмирати зависи од броја слободних пинова на чипу.

Понекад је довољан пин са аналогним подешавањем опсега програмабилних адреса, на пример САА1064 - драјвер ЛЕД индикатора који има управо такву имплементацију. Потенцијал одређеног пина одређује помак адресног простора чипа тако да се чипови истог типа не сукобљавају у раду на истој магистрали. Сви чипови који подржавају И2Ц магистралу садрже скуп адреса које произвођач наводи у документацији.

Комбинација «11110КСКС» је резервисана за 10-битно адресирање. Ако замислимо размену података са команде «СТАРТ» на команду «СТОП», то ће изгледати овако:

Овде су дозвољени једноставни и комбиновани формати размене података. Комбиновани формат значи да између «СТАРТ» и «СТОП» мастер и славе могу деловати као пријемници и предајници, што је корисно на пример у управљању серијском меморијом.

Нека први бајт података пренесе меморијску адресу. Затим, понављањем команде «СТАРТ» и читањем славе адресе, меморијски подаци ће радити. Одлуке о аутоматском повећању или смањењу адресе којој се претходно приступило доноси програмер уређаја након што је претходно проучио документацију чипа. На овај или онај начин, након што добију наредбу СТАРТ, сви уређаји морају вратити своју логику и припремити се за чињеницу да ће адреса сада бити именована.